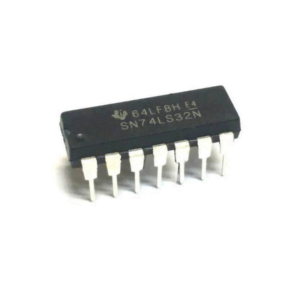

The 74LS107 designed as a JK Flip-Flop with individual J, K, Direct Clear, and Clock Pulse inputs. The Output changes are initiated by the HIGH-to-LOW transition of the clock. The J and K inputs must be stable one setup time before the high-to-low clock transition for predictable operation. The 74LS107 IC features a wide selection of working voltage, a good range of working conditions, and directly interfaces with CMOS, NMOS, and TTL.

The 74LS107 may be a dual in-line JK flip flop IC. It contains two independent J-K flip-flops with individual J-K, clock, and direct clear inputs. The 74LS73 is a positive pulse-triggered flip-flop. The J-K input data is loaded into the master while the clock is high and transferred to the slave and therefore the output on the high to low clock transition. For these devices, the J and K input must be stable while the clock is high. It operates at a military temperature over a variety of -55degree t 125 degrees C.

The JK Flip Flop designed as a gated RS flip flop with the addition of the clock input circuitry. When both the inputs S and R are adequate to logic “1”, the invalid condition takes place. Thus to stop this invalid condition, a clock circuit is introduced. The JK Flip Flop has four possible input combinations due to the addition of the clocked input. The four inputs are “logic 1”, ‘logic 0”. “No change’ and “Toggle”.

Applications

- They are utilized in digital clocks, electronic meters, and other electronic devices that display numerical information.

Reviews

There are no reviews yet.